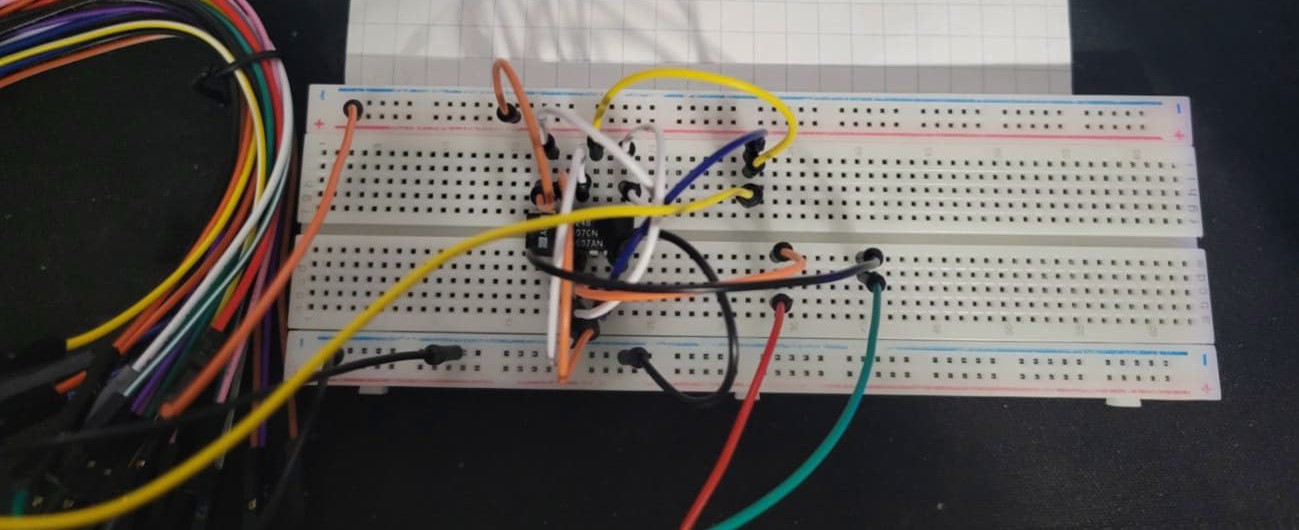

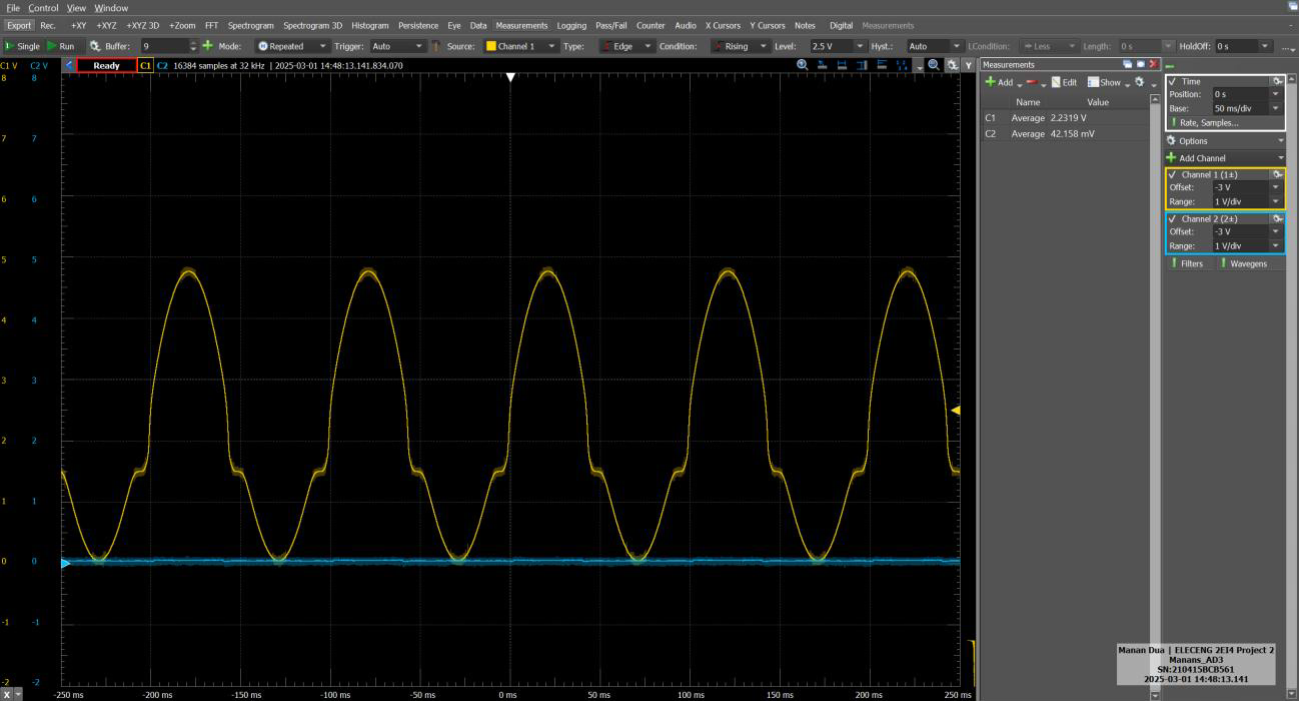

In this project, two voltage-controlled switches were designed, built, and tested using CD4007 MOSFET arrays. Each switch’s performance was evaluated against the ideal-switch model by examining four non-idealities: on-state resistance (Ron), off-state leakage (Roff), limited voltage range, and bidirectional capability. Measurements were compared to LTSpice simulations to understand practical deviations.

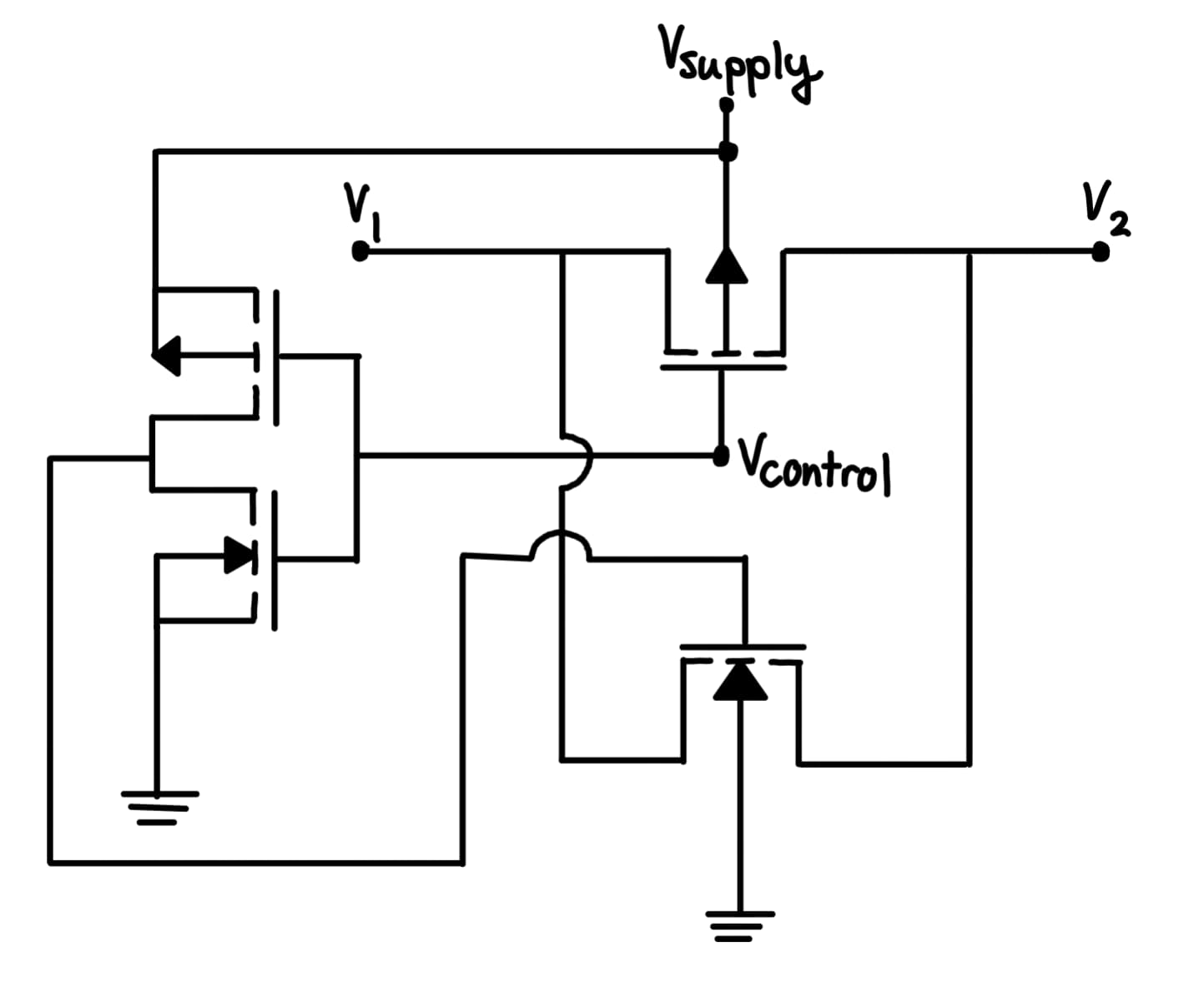

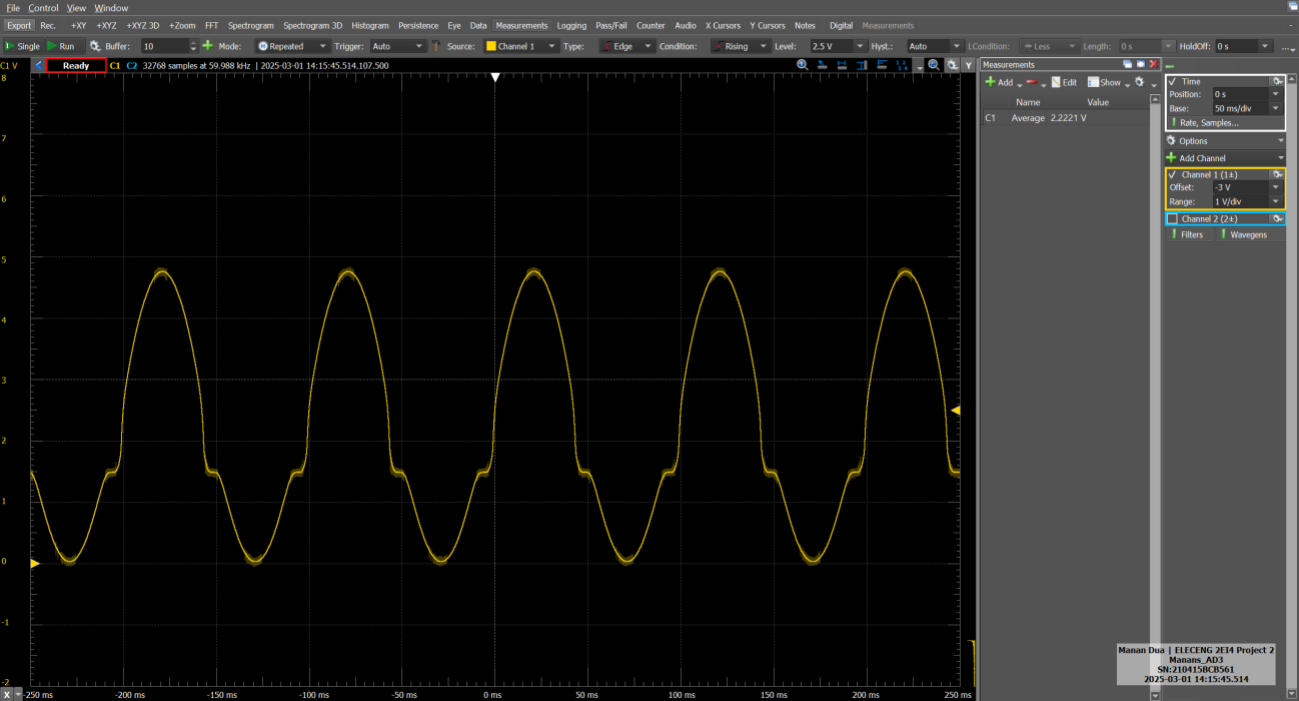

Switch Type 1: Single transmission gate formed by an NMOS and PMOS in parallel, controlled by Vcontrol and its inverse.

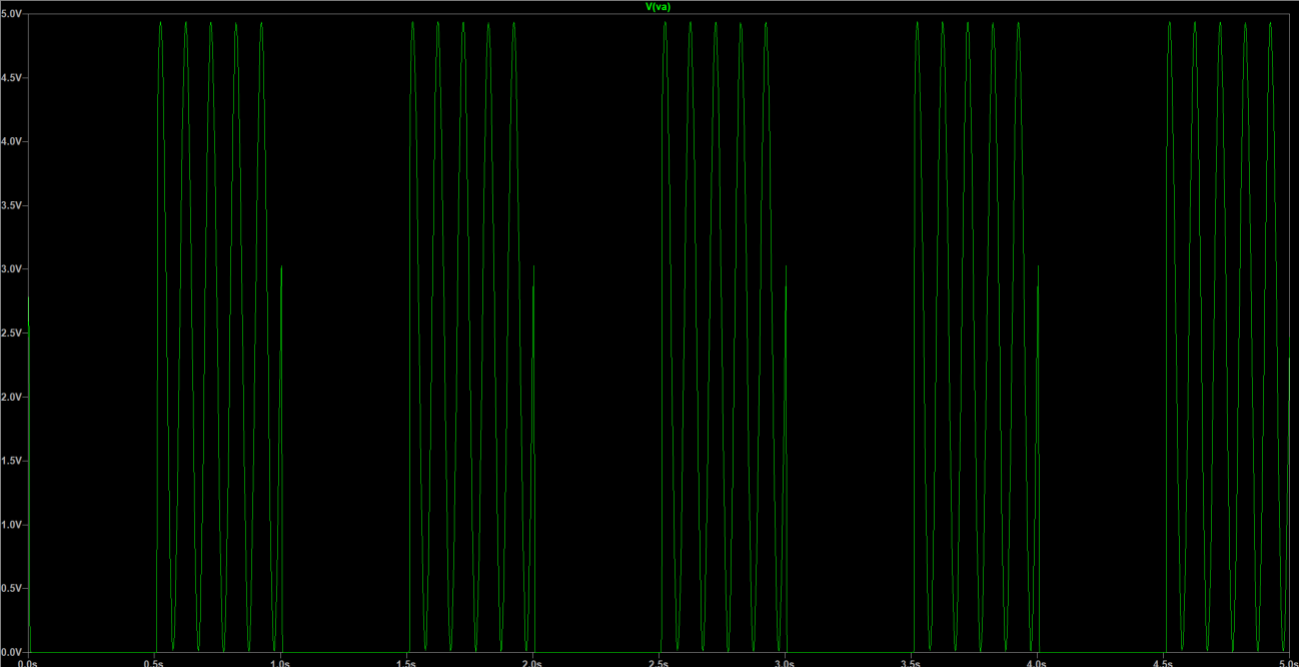

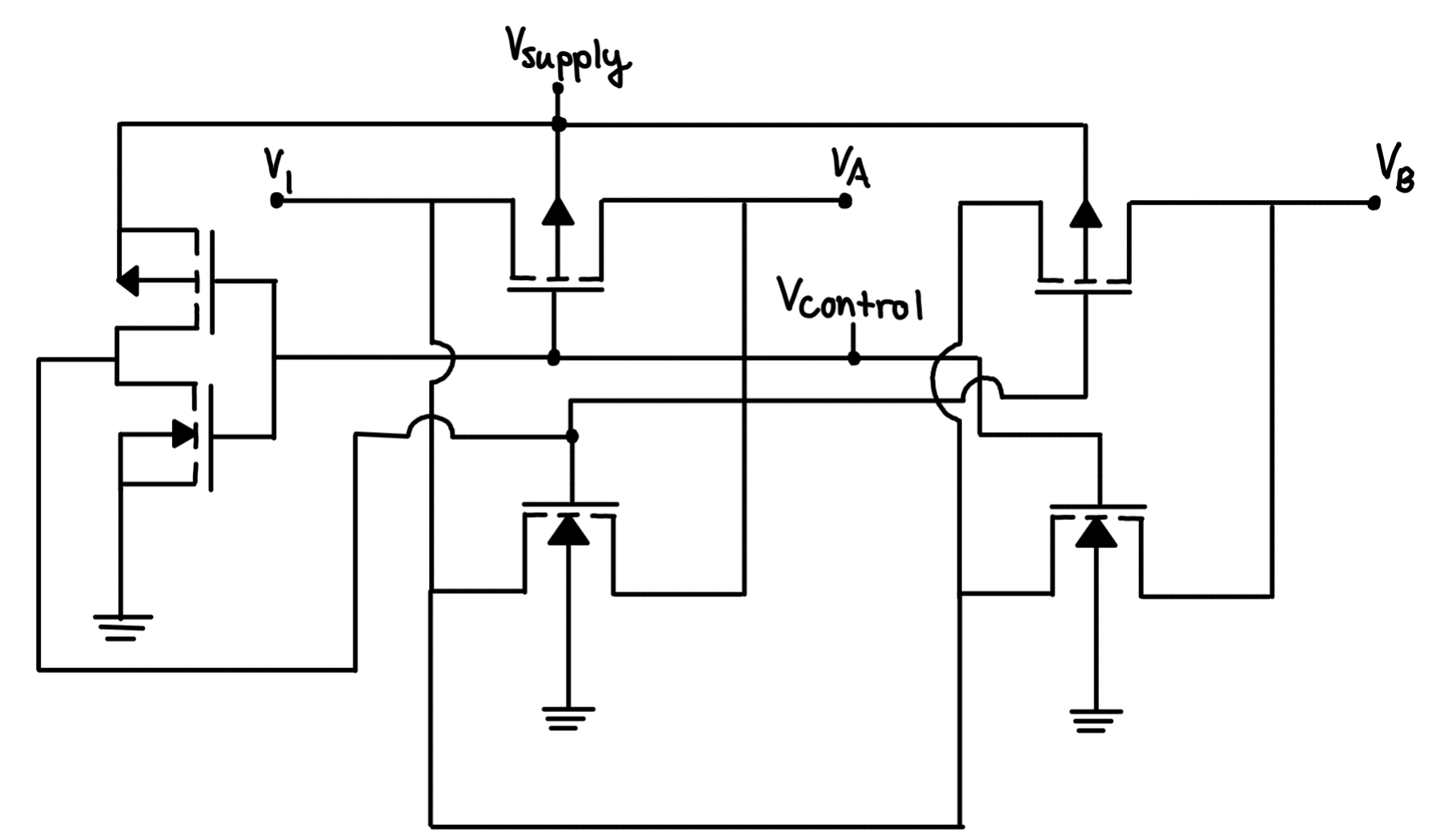

Switch Type 2: Two transmission gates arranged to select between two outputs (VA or VB), behaving like a 2:1 multiplexer.